Structure

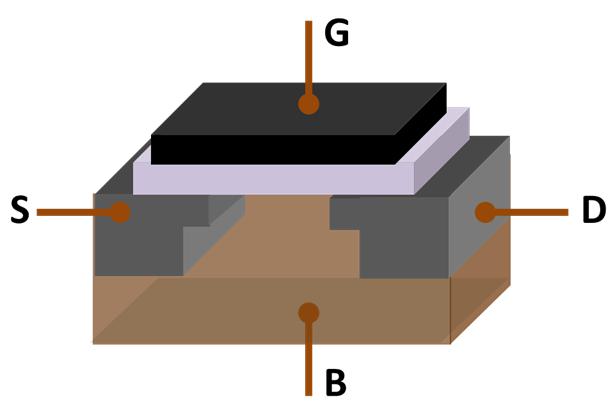

Figure 1 is a cross-sectional view of a typical planar N-channel enhancement mode NMOSFET. It uses a P-type silicon semiconductor material as a substrate, diffuses two N-type regions on its surface, and then covers a layer of silicon dioxide (SiO2) insulating layer, and finally it is made by etching above the N-region Two holes, using metallization method to make three electrodes on the insulating layer and in the two holes: G (gate), S (source) and D (drain), as shown in the figure. It can be seen from Figure 1 that the gate G is insulated from the drain D and the source S, and there are two PN junctions between D and S. Under normal circumstances, the substrate and the source are connected together internally, which is equivalent to a PN junction between D and S.

Figure 1 is the basic structure diagram of a common N-channel enhancement MOSFET. In order to improve the characteristics of certain parameters, such as increasing the working current, increasing the working voltage, reducing the on-resistance, and improving the switching characteristics, there are different structures and processes to form the so-called VMOS, DMOS, TMOS and other structures. Although there are different structures, their working principles are the same, so I won't introduce them one by one here.

Working principle

To make the enhanced N-channel MOSFET work, a positive voltage VGS must be added between G and S and a positive voltage VDS between D and S, then Generate positive working current ID. Changing the voltage of VGS can control the working current ID. As shown in Figure 2.

If VGS is not connected first (that is, VGS=0), a positive voltage VDS is added between the D and S poles, the PN junction between the drain D and the substrate is in the reverse direction, so the drain source There is no electricity between them. If a voltage VGS is applied between the gate G and the source S. At this time, the gate and the substrate can be regarded as the two plates of the capacitor, and the oxide insulating layer is used as the capacitor's dielectric. When VGS is added, positive charges are induced on the interface between the insulating layer and the gate, and negative charges are induced on the interface between the insulating layer and the P-type substrate. The negative charge induced in this layer is opposite to the polarity of the majority carriers (holes) in the P-type substrate, so it is called the "inversion layer". This inversion layer may divide the two N-type regions of the drain and the source. Connected to form a conductive channel. When the VGS voltage is too low, the negative charge induced is less, and it will be neutralized by the holes in the P-type substrate. Therefore, in this case, there is still no current ID between the drain and the source. When VGS increases to a certain value, the induced negative charge connects the two separated N regions to form an N channel. This critical voltage is called turn-on voltage (or threshold voltage, threshold voltage), which is represented by the symbol VT (generally stipulated VGS at ID=10uA is regarded as VT). When the VGS continues to increase, the negative charge increases, the conduction channel expands, and the resistance decreases, and the ID also increases, as shown in Figure 3. This curve is called the transfer characteristic. Therefore, within a certain range, it can be considered that changing the VGS to control the resistance between the drain and the source to achieve the effect of controlling the ID. Because of this structure when VGS=0, ID=0, this MOSFET is called an enhancement type. Another type of MOSFET also has a certain ID (called IDSS) when VGS=0. This type of MOSFET is called a depletion type. Its structure is shown in Figure 4, and its transfer characteristics are shown in Figure 5. VP is the pinch-off voltage (ID=0).

The main difference between the depletion type and the enhanced type is that there are a large number of positive ions in the manufacture of the SiO2 insulating layer, which induces more negative charges on the interface of the P-type substrate, that is, in the two N An N-type silicon thin layer is formed in the P-type silicon in the middle of the type region to form a conductive channel, so when VGS=0, there is a certain ID (IDSS) when VDS is active; when VGS has a voltage (it can be a positive voltage) Or negative voltage) to change the amount of negative charge induced, thereby changing the size of the ID. VP is -VGS when ID=0, which is called pinch-off voltage.

Detailed information

Overview

Looking at the naming of MOSFETs from the perspective of the name surface, in fact, people will get the wrong impression. Because the first letter M in MOSFET representing "metal" does not exist in most of the current components of the same kind. Early MOSFET gate electrode (gate electrode) used metal as its material, but with the advancement of semiconductor technology, later MOSFET gate uses polysilicon instead of metal. In processors, polysilicon gates are no longer the mainstream technology. Starting from Intel's P1266 processor with a 45-nanometer line width, the gates have begun to use metal again.

MOSFET is conceptually "Insulated-Gate Field Effect Transistor" (Insulated-Gate Field Effect Transistor, IGFET), and the gate insulating layer of IGFET may be other substances than the oxide layer used by MOSFET . Some people prefer to use IGFETs when referring to field-effect transistors with polysilicon gates, but most of these IGFETs refer to MOSFETs.

The oxide layer in the MOSFET is located above the channel. Depending on its operating voltage, the thickness of this oxide layer is only tens to hundreds of angstroms (Å). The material is usually silicon dioxide. (Silicon dioxide, SiO2), but some new advanced processes can already use silicon oxynitride (SiON) as the oxide layer.

Today’s semiconductor components are usually made of silicon (silicon), but some semiconductor companies have also developed processes that use other semiconductor materials. The most famous of these is IBM’s use of a mixture of silicon and germanium. The developed silicon-germanium process (SiGe process). It is a pity that many semiconductor materials with good electrical properties, such as gallium arsenide (GaAs), cannot be used to make MOSFET devices because they cannot grow a good-quality oxide layer on the surface.

When a large enough potential difference is applied between the gate and source of the MOSFET, the electric field will induce charges on the semiconductor surface under the oxide layer, and the so-called "reverse" The "inversion channel" will be formed. The polarity of the channel is the same as its drain and source. Assuming that the drain and source are N-type, then the channel will also be N-type. After the channel is formed, the MOSFET can allow current to pass, and depending on the voltage applied to the gate, the amount of current that can flow through the channel of the MOSFET will also be controlled by it.

Circuit Symbols

There are many variations of circuit symbols commonly used in MOSFETs. The most common design uses a straight line to represent the channel, and two lines perpendicular to the channel represent the source and drain. The pole, the shorter line on the left parallel to the channel represents the gate, as shown in the figure below. Sometimes the straight line representing the channel is replaced with a dashed line to distinguish between enhancement mode MOSFET (enhancement mode MOSFET) or depletion mode MOSFET (depletion mode MOSFET). In addition, it is divided into two types, NMOSFET and PMOSFET. The circuit symbol is shown in the figure. Show (the direction of the arrow is different).

Because the MOSFET on the integrated circuit chip is a four-terminal element, in addition to the gate, source, and drain, there is also a base (Bulk or Body). In the MOSFET circuit symbol, the direction of the arrow extending from the channel to the right can indicate that the component is an N-type or P-type MOSFET. The arrow direction always points from the P terminal to the N terminal, so the arrow pointing from the channel to the base terminal is a P-type MOSFET, or PMOS for short (the channel of this component is P-type); if the arrow points from the base to the channel, it represents the base. Extremely P-type, and the channel is N-type, this component is an N-type MOSFET, referred to as NMOS. In a general distributed MOSFET element (discrete device), the base and source are usually connected together, so the distributed MOSFET is usually a three-terminal element. The MOSFETs in integrated circuits usually use the same common bulk, so the polarity of the base is not marked, and a circle is added to the gate of the PMOS to show the difference (this is a foreign symbol, see the national standard symbol Figure).

In this way, MOSFET has 4 types: P-channel enhancement type, P-channel depletion type, N-channel enhancement type, N-channel depletion type, their circuit symbols and application characteristics The curve is shown in the figure below.

Principle of operation

The core of MOSFET: metal-oxide layer-semiconductor capacitor

Metal-oxide layer-semiconductor structure MOSFET has a metal-oxide structure in the structure Layer-semiconductor capacitance is the core (as mentioned earlier, most MOSFETs today use polysilicon instead of metal as their gate material), the oxide layer is mostly silicon dioxide, the bottom is silicon as the base, and the top It is polysilicon as the gate. Such a structure is exactly equal to a capacitor, the oxide layer plays the role of the dielectric material in the capacitor, and the capacitance value is determined by the thickness of the oxide layer and the dielectric constant of silicon dioxide. The gate polysilicon and base silicon become the two end points of the MOS capacitor.

When a voltage is applied across the MOS capacitor, the charge distribution of the semiconductor will also change. Consider a MOS capacitor formed by a P-type semiconductor (hole concentration is NA). When a positive voltage VGB is applied to the gate and base terminals (as shown in the figure), the concentration of holes will decrease and the concentration of electrons will increase. When the VGB is strong enough, the electron concentration near the gate terminal will exceed the hole. In a P-type semiconductor, the area where the concentration of electrons (with negative charges) exceeds the concentration of holes (with positive charges) is the so-called inversion layer.

The characteristics of the MOS capacitor determine the operating characteristics of the MOSFET, but a complete MOSFET structure also requires a source that provides a majority carrier and a drain that accepts these majority carriers.

Structure

A three-dimensional cross-sectional view of an NMOS transistor. The left picture is a cross-sectional view of an N-type MOSFET (hereinafter referred to as NMOS). As mentioned earlier, the core of the MOSFET is the MOS capacitor in the center, while the left and right sides are its source and drain. The characteristics of the source and drain must be both N-type (ie NMOS) or both P-type (ie PMOS). The "N+" marked on the source and drain of the NMOS in the right picture represents two meanings: ⑴N means doped impurity polarity in the source and drain regions is N; ⑵"+" means this region is Highly doped region (heavily doped region), that is, the electron concentration in this region is much higher than other regions. The source and drain are separated by an area of opposite polarity, which is the so-called base (or base) area. If it is NMOS, then the doping of the base region is P-type. On the contrary, for PMOS, the base should be N-type, while the source and drain are P-type (and heavy (pronounced as zhong) doped P+). The doping concentration of the substrate does not need to be as high as the source or drain, so there is no "+" in the picture on the right.

For this NMOS, only the surface area of the semiconductor directly below the MOS capacitor is actually used as a channel for carriers to pass through. When a positive voltage is applied to the gate, negatively charged electrons will be attracted to the surface, forming a channel, allowing the majority of N-type semiconductor carriers—electrons to flow from the source to the drain. If this voltage is removed, or a negative voltage is put on, then the channel cannot be formed, and the carriers cannot flow between the source and the drain.

Assuming that the object of operation is changed to PMOS, then the source and drain are P-type, and the substrate is N-type. When a negative voltage is applied to the gate of the PMOS, the holes on the semiconductor will be attracted to the surface to form a channel, and the majority of the semiconductor-holes can flow from the source to the drain. Assuming that this negative voltage is removed, or a positive voltage is added, then the channel cannot be formed, and there is no way for carriers to flow between the source and the drain.

In particular, the source in the MOSFET means "providing a source of majority carriers." For NMOS, most carriers are electrons; for PMOS, most carriers are holes. In contrast, the drain is the terminal that accepts majority carriers.

Main parameters

There are many parameters of field effect tubes, including DC parameters, AC parameters and limit parameters, but generally pay attention to the following main parameters:

1 , IDSS—Saturated drain-source current. It refers to the drain-source current when the gate voltage UGS=0 in the junction or depletion insulated gate field effect transistor.

2, UP—Pinch off voltage. It refers to the gate voltage when the drain-source is just cut off in the junction or depletion-type insulated gate field effect transistor.

3, UT—turn on the voltage. It refers to the gate voltage when the drain source is just turned on in the enhanced insulated gate field effect transistor.

4, gM—transconductance. It represents the gate-source voltage UGS—the ability to control the drain current ID, that is, the ratio of the change in the drain current ID to the change in the gate-source voltage UGS. gM is an important parameter to measure the amplification ability of the field effect tube.

5, BUDS—Drain-source breakdown voltage. It refers to the maximum drain-source voltage that the FET can withstand when the gate-source voltage UGS is constant. This is a limit parameter, and the working voltage applied to the FET must be less than BUDS.

6, PDSM—Maximum power dissipation. It is also a limiting parameter, which refers to the maximum allowable drain-source power dissipation when the performance of the field effect tube does not deteriorate. When in use, the actual power consumption of the field effect tube should be less than that of the PDSM and leave a certain margin.

7. IDSM—Maximum drain-source current. It is a limit parameter, which refers to the maximum current allowed to pass between the drain and the source when the FET is working normally. The working current of the FET should not exceed IDSM.

Model naming

Chinese naming method

There are two naming methods.

Field effect transistors usually have the following two naming methods.

The first naming method is to use the 3rd, 4th and 5th part of the "Chinese Semiconductor Device Model Nomenclature". The third part uses the letter CS to represent the field effect transistor, and the fourth part Some parts use Arabic numerals to indicate the device serial number, and the fifth part uses Chinese pinyin letters to indicate the specification number. E.g. CS2B, CS14A, CS45G, etc.

The second naming method is the same as that of bipolar transistors. The first digit uses a number to represent the number of electrodes; the second digit uses a letter to represent the polarity (where D is N channel and C is P channel) ; The third place uses letters to represent the type (where J stands for junction field effect transistors, and O stands for insulated gate field effect transistors). For example, 3DJ6D is an N-channel junction field effect transistor, and 3D06C is an N-channel insulated gate field effect transistor.

Japanese nomenclature

Semiconductor discrete devices produced in Japan consist of five to seven parts. Usually only the first five parts are used, and the symbol meaning of each part is as follows:

Part 1: Use numbers to indicate the number or type of effective electrodes of the device. 0-photoelectric (ie photosensitive) diode triode and the combination of the above devices, 1-diode, 2 triode or other devices with two pn junctions, 3- other devices with four effective electrodes or three pn junctions, ┄┄and so on.

Part II: Japan Electronics Industry Association JEIA registered mark. S- represents a semiconductor discrete device registered with the Japan Electronics Industry Association JEIA.

Part 3: Use letters to indicate the polarity and type of materials used in the device. A-PNP type high frequency tube, B-PNP type low frequency tube, C-NPN type high frequency tube, D-NPN type low frequency tube, FP control pole SCR, GN control pole SCR, HN base single junction transistor , JP channel field effect tube, KN channel field effect tube, M-triac.

Part 4: Use numbers to indicate the serial number registered in the Japan Electronics Industry Association JEIA. Two or more integers-starting from "11", it represents the serial number registered in the Japan Electronics Industry Association JEIA; devices with the same performance from different companies can use the same serial number; the larger the number, the more recent products.

Part 5: Use letters to indicate the improved product logo of the same model. A, B, C, D, E, F indicate that this device is an improved product of the original model product.

For example, 2SK134 is an N-channel MOSFET, and 2SJ49 is a P-channel MOSFET.

Application advantages

1. Field-effect transistors are voltage control elements, while bipolar junction transistors are current control elements. In the case of only allowing less current to be drawn, a field effect transistor should be used; and in the case of a lower signal voltage and allowing more current to be drawn from the signal source, a bipolar transistor should be used.

2. The source and drain of some FETs can be used interchangeably, and the gate voltage can also be positive or negative, which is more flexible than bipolar transistors.

3. FETs use majority carriers to conduct electricity, so they are called unipolar devices, while bipolar junction transistors have majority carriers and minority carriers to conduct electricity. . Therefore it is called a bipolar device.

4. The field effect transistor can work under very small current and very low voltage, and its manufacturing process can easily integrate many field effect transistors on a silicon chip, so the field effect Tubes have been widely used in large-scale integrated circuits.

MOSFET was first implemented successfully by D. Kahng and Martin Atalla of Bell Lab. in 1960. The operating principle of this component was invented by William Shockley and others in 1947. The Bipolar Junction Transistor (BJT) is completely different, and because of the advantages of low manufacturing cost, small use area, and high integration, it is used in large-scale integrated circuits (Large-Scale Integrated Circuits, LSI) or In the field of Very Large-Scale Integrated Circuits (VLSI), it is far more important than BJT.

As the performance of MOSFET components is gradually improving, in addition to traditional applications such as microprocessors, microcontrollers and other digital signal processing applications, there are also more and more analog signal processing integrated circuits that can use MOSFETs. To achieve, these applications are introduced below.

Digital circuit

Digital Advances in technology, such as the continuous improvement of microprocessor computing performance, give more power to the in-depth research and development of a new generation of MOSFET. It also makes the operation speed of MOSFET itself faster and faster, almost becoming the fastest one of various semiconductor active components. The main success of MOSFETs in digital signal processing comes from the invention of CMOS logic circuits. The biggest advantage of this structure is that there is no static power loss in theory, only in logic gates. Electric current flows only when switching action. The most basic member of CMOS logic gates is the CMOS inverter (inverter), and the basic operation of all CMOS logic gates is the same as an inverter. There must be only one type of transistor (NMOS or PMOS) at the same time at the moment of logic conversion. In the on state, the other must be off state, which makes there is no direct conduction path from the power terminal to the ground terminal, which saves a lot of current or power consumption, and also reduces the heat generation of the integrated circuit. .

Another major advantage of MOSFETs in digital circuits is that for direct current (DC) signals, the gate impedance of the MOSFET is infinite (equivalent to an open circuit), that is, theoretically there will be no The current flows from the gate terminal of the MOSFET to the ground point in the circuit, but the gate is completely controlled by the voltage. This makes MOSFETs more power efficient and easier to drive than their main competitor BJT. In CMOS logic circuits, except for the driver responsible for driving off-chip loads, the logic gates of each level only need to face the gate of the same MOSFET, so there is less need to consider logic The driving force of the door itself. In contrast, BJT's logic circuit (such as the most common TTL) does not have these advantages. The infinite gate input resistance of the MOSFET also has other advantages for the circuit design engineer, for example, it is less necessary to consider the loading effect at the output of the logic gate.

Analog Circuits

For a while, MOSFETs were not the first choice of analog circuit design engineers, because analog circuit design values the performance parameters, such as the transconductance of transistors or current In terms of driving force, MOSFET is not as suitable as BJT for the needs of analog circuits. However, with the continuous evolution of MOSFET technology, today's CMOS technology can already meet the specification requirements of many analog circuits. In addition, because of the structure of the MOSFET, there are no fatal shortcomings of BJT, such as thermal runaway. In addition, the voltage-controlled resistance characteristics of MOSFETs in the linear region can also be used in integrated circuits to replace traditional poly resistors, or MOS capacitors themselves can be used to replace common polysilicon-insulator-polysilicon capacitors (PIP capacitor) , Even under proper circuit control, it can show the characteristics of inductance (inductor), these benefits are difficult for BJT to provide. In other words, in addition to playing the role of the original transistor, MOSFET can also be used as a passive device (passive device) widely used in analog circuits. This advantage allows the use of MOSFETs to implement analog circuits not only to meet the requirements of specifications, but also to effectively reduce the area of the chip and reduce production costs.

With the advancement of semiconductor manufacturing technology, the demand for integrating more functions into a single chip has also increased significantly. At this time, another advantage of using MOSFETs to design analog circuits has also emerged. In order to reduce the number of integrated circuits used on the Printed Circuit Board (PCB), reduce packaging costs and reduce the size of the system, many originally independent analog chips and digital chips are integrated into the same chip. MOSFET originally had a great competitive advantage in digital integrated circuits, and after a large number of MOSFETs were used in analog integrated circuits, the difficulty of integrating these two circuits with different functions has also decreased significantly. In addition, some mixed-signal circuits, such as Analog-to-Digital Converter (ADC), can also use MOSFET technology to design products with better performance.

There is also a process technology that integrates the advantages of MOSFET and BJT: BiCMOS (Bipolar-CMOS) is becoming more and more popular. BJT components are still better than ordinary CMOS in their ability to drive large currents, and they also have some advantages in terms of reliability, such as not being easily damaged by "electrostatic discharge" (ESD). Therefore, many integrated circuit products that require complex noise signal processing and strong current drive capability will be manufactured using BiCMOS technology.

Size scaling

In the past decades, the size of MOSFETs has continued to shrink. In the early MOSFET manufacturing process of integrated circuits, the channel length was on the order of several micrometers. But in today's integrated circuit manufacturing process, this parameter has shrunk dozens of times or even more than a hundred times. In early 2006, Intel began to manufacture a new generation of microprocessors with 65 nanometer (nanometer) technology. The actual component channel length may be smaller than this number. By the end of the 1990s, the MOSFET size continued to shrink, greatly improving the performance of integrated circuits. From a historical perspective, these technological breakthroughs are closely related to the progress of semiconductor manufacturing processes.

Why shrink the size of MOSFET

Based on the following reasons, we hope that the size of MOSFET can be as small as possible. First, a smaller MOSFET means that its channel length is reduced, and the equivalent resistance of the channel is also reduced, allowing more current to pass. Although the channel width may also become smaller and the equivalent resistance of the channel becomes larger, if the unit resistance can be reduced, then this problem can be solved. Secondly, the smaller size of the MOSFET means that the gate area is reduced, which can reduce the equivalent gate capacitance. In addition, a smaller gate usually has a thinner gate oxide layer, which can reduce the unit resistance of the aforementioned channel. However, such a change will also make the gate capacitance become larger, but compared with the reduced channel resistance, the benefits are still more than the disadvantages, and the switching speed of the MOSFET after the size is reduced will also be increased due to the above two factors. Always faster. The third reason is that the smaller the area of the MOSFET, the cost of manufacturing chips can be reduced, and higher-density chips can be installed in the same package. The wafer size used in a piece of integrated circuit manufacturing process is fixed, so if the chip area is smaller, the same size wafer can produce more chips, so the cost becomes lower.

Although MOSFET size reduction can bring many benefits, it also has many negative effects.

Difficulties after the size of MOSFET is reduced

Shrinking the size of MOSFET to less than one micron is a challenge for the semiconductor process, but most of the new challenges come from smaller and smaller sizes. Physical effects brought about by MOSFET components have never appeared in the past.

Sub-threshold conduction

As the thickness of the MOSFET gate oxide layer is also continuously reduced, the upper limit of the gate voltage is also reduced to avoid Excessive voltage causes breakdown of the gate oxide layer. In order to maintain the same performance, the critical voltage of the MOSFET must also be lowered, but this also makes it increasingly difficult for the MOSFET to turn off completely. In other words, the gate voltage sufficient to cause weak inversion of the MOSFET channel region will be lower than before, so the so-called subthreshold current will cause more serious problems than in the past, especially today's integrated circuit chips. The number of transistors contained has increased dramatically. In some VLSI chips, the power consumption caused by sub-threshold conduction accounts for more than half of the total power consumption.

But on the other hand, some circuit designs will benefit from the sub-threshold conduction of MOSFETs. For example, in circuits that require a higher transconductance-to-current ratio, Designs that use sub-threshold conduction MOSFETs to achieve their goals are also quite common.

The parasitic capacitance effect of the connecting wires inside the chip

Traditionally, the switching speed of CMOS logic gates is related to the gate capacitance of its components. However, when the gate capacitance decreases as the size of the MOSFET becomes smaller, and more transistors can be accommodated on the same size chip, the parasitic capacitance effect generated between the metal wires connecting these transistors begins to dominate the switching speed of the logic gate. How to reduce these parasitic capacitances has become one of the keys to the improvement of chip efficiency.

The heat generation of the chip increases

When the number of transistors on the chip increases significantly, an unavoidable problem also occurs, that is, the chip’s The calorific value also increased significantly. The operation of general integrated circuit components at high temperatures may affect the switching speed, or cause reliability and lifetime problems. In some integrated circuit chips with very high heat generation, such as microprocessors, an additional heat dissipation system is needed to alleviate this problem.

In the field of Power MOSFET, the channel resistance often increases due to the increase in temperature, which also increases the power loss caused by the pn-junction in the component . Assuming that the external heat dissipation system cannot keep the temperature of the power transistors low enough, it is likely that these power transistors will suffer thermal runaway fate.

The leakage current of the gate oxide increases

As the size of the MOSFET becomes smaller, the gate oxide becomes thinner and thinner. In the mainstream semiconductor manufacturing process, Even a gate oxide layer with a thickness of only 1.2 nanometers has been made, which is approximately equal to the thickness of 5 atoms stacked together. At this scale, all physical phenomena are within the world regulated by quantum mechanics, such as the tunneling effect of electrons (tunneling effect). Due to the tunneling effect, some electrons have the opportunity to cross the potential barrier formed by the oxide layer and generate leakage current, which is also one of the sources of power consumption in today's integrated circuit chips.

In order to solve this problem, some materials with a higher dielectric constant than silicon dioxide are used in the gate oxide layer. For example, metal oxides (hafnium dioxide, zirconium dioxide) and other high dielectric constant materials of hafnium and zirconium can effectively reduce the gate leakage current. After the dielectric constant of the gate oxide layer is increased, the thickness of the gate can be increased to maintain the same capacitance. The thicker gate oxide layer can reduce the probability of electrons passing through the oxide layer through the tunneling effect, thereby reducing leakage current. However, the gate oxide layer made of new materials must also consider the height of its potential energy barrier, because the conduction band and valence band of these new materials and the gap between the conduction band and the valence band of the semiconductor are more than two. Silicon oxide is small (the height difference between the conduction band of silicon dioxide and silicon is about 8ev), so it is still possible to cause gate leakage current.

Process variations are more difficult to control

Modern semiconductor manufacturing processes are complex and numerous. Any process may cause the components on the integrated circuit chip to produce a little Variation. When MOSFETs and other components become smaller and smaller, the proportion of these variations may increase significantly, which in turn affects the performance expected by the circuit designer. Such variations make the work of the circuit designer more difficult.

MOSFET gate material

Theoretically, the gate of MOSFET should choose a conductor with good electrical properties as much as possible. The conductivity of polysilicon after heavy (pronounced as zhong) doping It can be used on the gate of a MOSFET, but it is not a perfect choice. The reason why MOSFET uses polysilicon is as follows:

⒈ The threshold voltage of MOSFET is mainly determined by the difference between the work function of the gate and channel material, and because polysilicon is essentially It is a semiconductor, so its work function can be changed by doping with impurities of different polarity. More importantly, because the bandgap between polysilicon and the silicon underneath is the same, it is possible to directly adjust the work function of polysilicon to meet the demand when reducing the threshold voltage of PMOS or NMOS. Conversely, the work function of metal materials is not as easy to change as semiconductors, so it becomes more difficult to reduce the critical voltage of MOSFET. Moreover, if you want to reduce the threshold voltage of PMOS and NMOS at the same time, you will need two different metals as the gate materials, which is a big variable for the manufacturing process.

⒉ After years of research on the silicon-silicon dioxide junction, it has been confirmed that the defects between these two materials are relatively few. On the contrary, there are many defects in the metal-insulator interface, which easily form many surface energy levels between the two, which greatly affects the characteristics of the device.

⒊ Polysilicon has a higher melting point than most metals, and it is customary to deposit gate materials at high temperatures in modern semiconductor manufacturing processes to improve device performance. The low melting point of the metal will affect the upper limit of the temperature that can be used in the process.

Although polysilicon has been the standard for manufacturing MOSFET gates in the past two decades, there are still several shortcomings that make it possible for some MOSFETs to use metal gates in the future. These shortcomings are as follows:

⒈ Polysilicon is not as conductive as metal, which limits the speed of signal transmission. Although the conductivity can be improved by doping, the effect is still limited. Some metal materials with a relatively high melting point, such as tungsten (Tungsten), titanium (Titanium), cobalt (Cobalt) or nickel (Nickel), are used to make alloys with polysilicon. This type of hybrid material is often called a silicide. The polysilicon gate with metal silicide added has good electrical conductivity and can withstand high-temperature manufacturing processes. In addition, because the location of the metal silicide is on the gate surface, far from the channel area, it will not have much impact on the threshold voltage of the MOSFET.

The process of plating metal silicide on the gate, source and drain is called "Self-Aligned Silicide" (Self-Aligned Silicide), usually referred to as the salicide process.

⒉ When the size of the MOSFET shrinks very small and the gate oxide layer becomes very thin, for example, the latest process at the time of editing this article can shrink the oxide layer to a thickness of about one nanometer. The phenomenon that has not been found also arises, this phenomenon is called "polysilicon depletion." When the inversion layer of the MOSFET is formed, where the polysilicon of the MOSFET gate with polysilicon depletion is close to the oxide layer, a depletion layer will appear, which affects the conduction characteristics of the MOSFET. To solve this problem, a metal gate is the best solution. Possible materials include Tantalum, Tungsten, Tantalum Nitride, or Titanium Nitride. These metal gates usually form a MOS capacitor together with an oxide layer formed from a high dielectric constant material. Another solution is to completely alloy polysilicon, which is called FUSI (FUlly-SIlicide polysilicon gate) process.

Various common MOSFET technologies

Dual-gate MOSFET

Dual-gate MOSFET is usually used in radio frequency (RF) In integrated circuits, both gates of this MOSFET can control the current. In the application of radio frequency circuits, the second gate of a double-gate MOSFET is mostly used for gain, mixer or frequency conversion control.

Depletion mode MOSFET

Generally speaking, a depletion mode MOSFET is less common than the aforementioned enhancement mode MOSFET. The depletion type MOSFET changes the impurity concentration doped into the channel during the manufacturing process, so that even if the gate of this MOSFET is not applied with voltage, the channel still exists. If you want to turn off the channel, you must apply a negative voltage to the gate. The largest application of depletion MOSFETs is in "normally-off" switches, while enhanced MOSFETs are used in "normally-on" switches.

NMOS logic

NMOS with the same drive capability usually occupies a smaller area than PMOS, so if only NMOS is used in the design of logic gates, the chip area can be reduced. However, although NMOS logic occupies a small area, it cannot consume static power like CMOS logic. Therefore, it has gradually withdrawn from the market after the mid-1980s.

Power MOSFET

A cross-sectional view of the power transistor unit. Usually a commercially available power transistor contains thousands of such units. Main article: Power Transistor

There is a significant difference in structure between the power MOSFET and the aforementioned MOSFET components. Generally, MOSFETs in integrated circuits have a planar structure, and each end point in the transistor is only a few microns away from the chip surface. And all power components are vertical (vertical) structure, so that components can withstand high voltage and high current working environment at the same time. The voltage that a power MOSFET can withstand is a function of the impurity doping concentration and the thickness of the N-type epitaxial layer, and the current that can pass is related to the channel width of the device. The wider the channel, the more current it can accommodate. For a MOSFET with a planar structure, the amount of current and breakdown voltage that it can withstand is related to the length and width of its channel. For a MOSFET with a vertical structure, the area of the device is approximately proportional to the current it can hold, and the thickness of the epitaxial layer is proportional to its breakdown voltage.

Working principle of power MOSFET

Off: A positive power supply is added between the drain and the source, and the voltage between the gate and the source is zero. The PN junction J1 formed between the P base region and the N drift region is reverse biased, and no current flows between the drain and the source.

Conduction: Apply a positive voltage UGS between the gate and source, the gate is insulated, so no gate current will flow. But the positive voltage of the gate will push away the holes in the P region below it, and the minority electrons in the P region will be attracted to the surface of the P region below the gate

When UGS is greater than UT (turn on Voltage or threshold voltage), the electron concentration on the surface of the P region under the gate will exceed the hole concentration, making the P-type semiconductor inverted into an N-type to become an inversion layer, which forms an N channel and makes the PN junction J1 Disappear, the drain and source are conductive.

It is worth mentioning that the use of planar power MOSFETs is not absent, and these components are mainly used in advanced audio amplifiers. The planar power MOSFET has better characteristics in the saturation region than the vertical structure MOSFET. Vertical power MOSFETs take the advantage of very small turn-on resistance, and are mostly used for switching.

DMOS

DMOS is the abbreviation of double-diffused MOSFET (double-Diffused MOSFET), which is mainly used for high voltage and belongs to the category of high voltage MOS tube.

Realize analog switch with MOSFET

The channel resistance of MOSFET is low when it is turned on, and the resistance when it is turned off is almost infinite, so it is suitable as a switch for analog signals (the energy of the signal is not It will lose too much due to the resistance of the switch). When a MOSFET is used as a switch, the difference between its source and drain is not the same as other applications, because the signal can enter and exit from any end other than the MOSFET gate. For NMOS switches, the most negative side of the voltage is the source, while PMOS is the opposite, and the most positive side is the source. The signal that a MOSFET switch can transmit is limited by its gate-source, gate-drain, and drain-to-source voltage. If the upper limit of the voltage is exceeded, it may cause the MOSFET to burn.

The application range of MOSFET switches is very wide. For example, the design of sample-and-hold circuits or chopper circuits, such as analog-to-digital converters (A /D converter) or switch-capacitor filter (switch-capacitor filter), you can see the trace of MOSFET switch.

Single MOSFET switch

When NMOS is used as a switch, its base is grounded and the gate is the end point of the control switch. When the gate voltage minus the source voltage exceeds its turn-on threshold voltage, the state of the switch is turned on. If the gate voltage continues to rise, the current that the NMOS can pass will increase. NMOS operates in the linear region when switching, because the voltages of the source and drain tend to be the same when the switch is on.

When PMOS is used as a switch, its base is connected to the highest potential in the circuit, which is usually the power supply. When the gate voltage is lower than the source and exceeds its critical voltage, the PMOS switch will turn on.

The upper limit of the voltage allowed by the NMOS switch is (Vgate-Vthn), while the PMOS switch is (Vgate+Vthp). This value is usually not the original voltage amplitude of the signal, which means that a single MOSFET switch will There are disadvantages of making the signal amplitude smaller and distorting the signal.

Double MOSFET (CMOS) switch

In order to improve the shortcomings of signal distortion caused by the aforementioned single MOSFET switch, the use of a PMOS plus an NMOS CMOS switch has become the most common practice. The CMOS switch connects the source and drain of the PMOS and NMOS respectively, and the connection of the base is the same as the traditional connection of NMOS and PMOS. When the input voltage is between (VDD-Vthn) and (VSS+Vthp), both PMOS and NMOS are on, and when the input is less than (VSS+Vthp), only NMOS is on, and when the input is greater than (VDD-Vthn), only PMOS is on. Pass. The advantage of this is that under most input voltages, both PMOS and NMOS are turned on at the same time. If the on-resistance of either side increases, the on-resistance of the other side will decrease, so the resistance of the switch can almost be kept constant. , Reduce signal distortion.

Contrast

Power MOSFET stands for power field effect transistor. Its three poles are source (S), drain (D) and gate (G). Main advantages: good thermal stability and large safe working area. Disadvantages: low breakdown voltage and low working current. IGBT stands for insulated gate bipolar transistor, which is a combination of MOSFET and GTR (power transistor). Its three poles are collector (C), emitter (E) and grid (G). Features: The breakdown voltage can reach 1200V, and the maximum saturation current of the collector has exceeded 1500A. The inverter with IGBT as the inverter device has a capacity of over 250kVA and an operating frequency of up to 20kHz.