Concept

Direct memory access method is mainly used for the rapid device and the main memory into batch exchange data. In this application, the starting point of the processing problem is set to two: First, the data that cannot be lost, the second is to further reduce the disturbance of the CPU during the operation of the fast device. This can be controlled by handling the transfer process of this batch of data, allowing the DMA card to directly transmit data directly between the CPU to control between the fast device and the main memory, and only one data is transmitted. A bus cycle can be. From the perspective of common use bus, DMA and CPU become a competitor relationship. When a batch of data is completed, the fast device still wants to send a request to the CPU, and reports the "Reputation" next operational requirements while reporting the end of this transfer.

Features

PIO mode The data transfer between the hard disk and the memory is controlled by the CPU; in the DMA mode, the CPU only needs to decide to the DMA controller, let The DMA controller processes the transfer of data, and the data transfer is fed back to the CPU, which greatly reduces the CPU resource share. The difference between the DMA mode and PIO mode is that the DMA mode does not depend on the CPU, which can save system resources, and the difference between the two is not very obvious. The DMA mode can be divided into two kinds of Single-Word DMA (single-byte DMA) and Multi-Word DMA (multi-byte DMA), where the maximum transmission rate that can be achieved is only 16.6Mb / s.

DMA transfer method is higher than the program interrupt, and the difference between the two is mainly different from the degree of interference of the CPU. The program interrupt request not only causes the CPU to stop, but also to execute the interrupt service program for the Interrupt Request service, including the processing of breakpoints and field processing and CPU and peripherals, so the CPU pays a lot of cost; DMA request Only the CPU is paused, does not require processing of the breakpoint and the site, and is transmitted between the DMA control peripherals and the main memory, without the intervention of the CPU, DMA only borrows a point of CPU. There is also a difference that the CPU is different from the response time of the two requests, and the program interrupt request generally responds to the clock cycle of the execution of one instruction, and the request for DMA, because of its efficiency, CPU is in each All stages performed by the article instructions can be used to use the DMA, which is an immediate response. The DMA is mainly implemented by hardware. At this time, data exchange between high-speed peripherals and memory is not controlled by the CPU, but the system bus. The DMA method is one of the main ways of I / O systems and host exchange data, and there are program query and interrupt mode.

DMA Working principle

DMA is an important feature of all modern computers, which allows different speed hardware devices to communicate without the need to be in large number of interrupt loads in the CPU. Otherwise, the CPU needs to copy the information of each piece to the scratcher from the source and then write them back to the new place. In this time, the CPU cannot be used for other work.

DMA transmission is important to copy a memory area from one device to another. When the CPU initializes this transmission action, the transmission action itself is implemented and completed by the DMA controller. A typical example is to move an external memory block to the faster memory in the chip. Like this operation does not allow the processor to delay, but can be re-scheduled to deal with other work. DMA transmission is important for high performance embedded system algorithms and networks.

Example

For example, the PC ISA DMA controller has 8 DMA channels, and 7 channels are available to the CPU of the PC. Each DMA channel has a 16-bit unit register and a 16-bit count specuse. When the data is initialized, the device driver sets the location of the DMA channel and the counting register, as well as the direction, reading, or writing of data transfer. Then indicate that the DMA hardware starts this transmission action. When the transmission ends, the device will notify the CPU in a interrupted manner.

"Scatter-Gather) DMA allows data to multiple memory regions to be transferred in a single DMA process. It is equivalent to stringing multiple simple DMAs. Once again, this motive is to reduce the multi-output input interrupt and data replication task of the CPU.

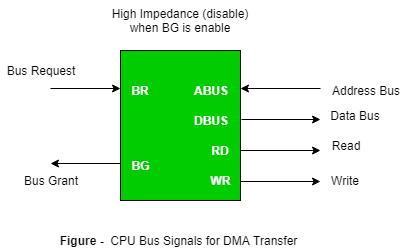

DRQ means DMA requirements; DACK means that DMA is confirmed. These symbols can be seen on a computer system hardware overview with a DMA function. They represent the electronic signal transmission line between the CPU and the DMA controller.